火热开赛,第五届集成电路EDA设计精英挑战赛概伦电子赛题发布

2023-08-22

近日,第五届集成电路EDA设计精英挑战赛正式拉开帷幕。作为国内首家EDA上市公司,也是集成电路设计自动化(EDA)产教融合联盟常务理事单位,概伦电子一直秉持与中国集成电路产业共同成长的理念,始终致力于为中国集成电路产业打造多层次的专业人才培养机制,已连续五年支持和参与该项赛事。本次概伦电子全新发布“标准单元电路的版图自动生成”企业赛题,欢迎广大同学们踊跃报名!

赛题名称

标准单元电路的版图自动生成

赛题背景

在数字电路标准单元库的开发中,版图设计是最重要的环节之一。目前标准单元的版图绘制仍然以人工绘制为主,而库中单元的数量往往多达上千颗,导致整个标准单元库的开发周期较长。如果能够提高标准单元版图设计自动化的程度,整个库的开发周期将大大缩减。

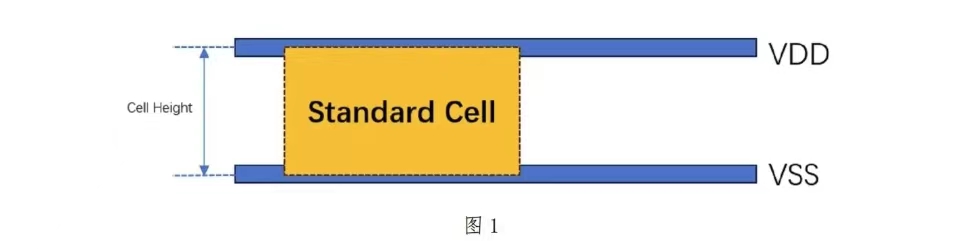

标准单元的版图设计中,通常包含两个环节——晶体管布局和布线。本赛题重点关注布局环节,主要考虑组合逻辑和时序逻辑的标准单元,包含NMOS 和 PMOS 晶体管。在本题中,平面工艺下简化后的布局问题如图1所示,标准单元将被放在两条电源轨道(Power Rail)之间,高度固定,宽度不定。

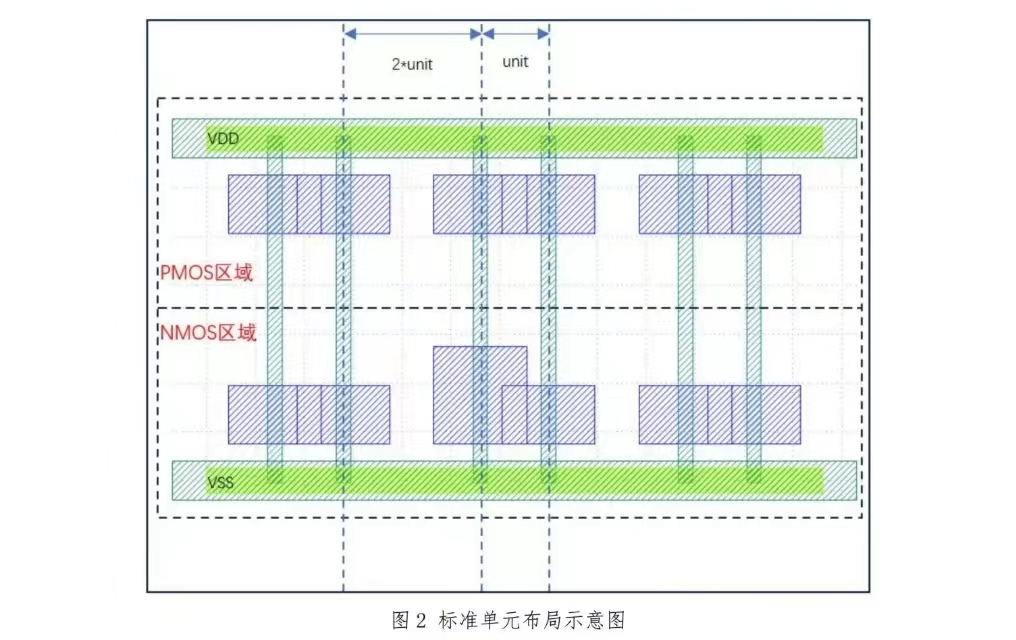

在标准单元的内部,晶体管按两行依次放置,PMOS晶体管在上面一行,NMOS 晶体管放在下面一行,本题中所有晶体管的有源区向电源轨道对齐,如图 2,详细描述见赛题描述。

注:1. 晶体管由两个矩形表示,垂直矩形为栅极,蓝色矩形为有源区。2. 图中上下两侧的绿色矩形为电源轨道,分别连接VDD 和VSS。3. 整个标准单元被等分为两个部分,上半部分为PMOS 晶体管可放置的区域,下半部分为 NMOS 晶体管可放置的区域。4. 所有晶体管有源区向两侧的电源轨道对齐。5. 同一水平位置的晶体管栅极会直接相连。6. 若两个晶体管的有源区重叠,则其栅极间距为1个单位长度,此时要求重叠部分所连线网相同;若不重叠,则其栅极间距至少为2个单位长度。7. 本题中任意两个晶体管的栅极间距都为整数个单位长度。

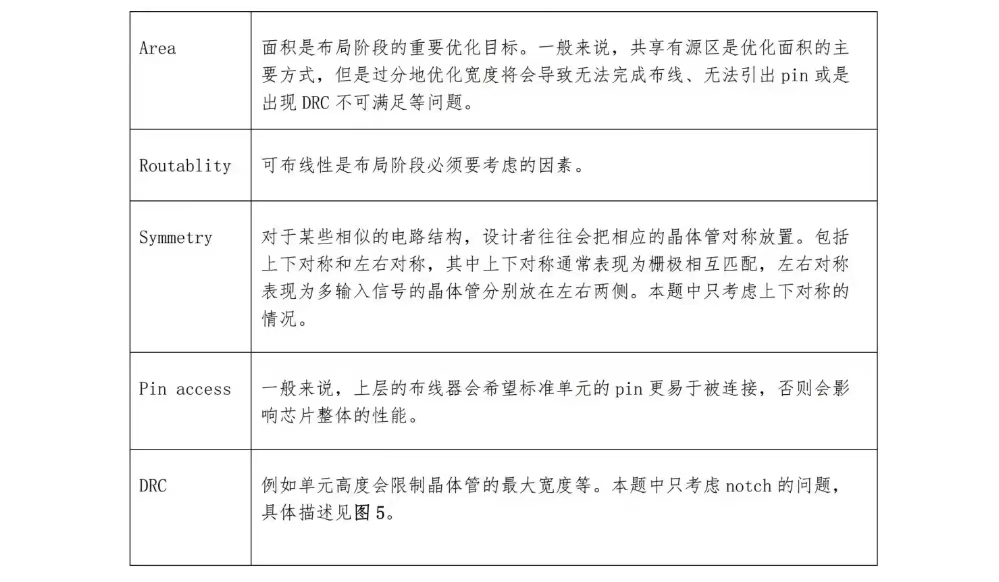

在进行晶体管布局时,版图工程师通常需要考虑以下这些内容:

在现有的标准单元布局算法的研究中,对面积和可布线性的优化算法已经有较多的参考。但是由于缺乏对其他内容的考虑,算法自动生成的布局通常无法直接被使用,尤其是在一些较为复杂的标准单元中,版图工程师往往需要花上 1-2 周的时候去调整和优化布局。

赛题Chair介绍

叶佐昌

清华大学

博士,毕业于清华大学微电子研究所。曾在美国Cadence伯克利实验室担任研究员,目前为清华大学集成电路学院副研究员,研究领域包括集成电路仿真、建模和自动化设计方法学。目前研究方向主要用于模拟全流程敏捷设计的EDA工具开发。

赛题描述

请查看完整版赛题描述:

大赛概况

2023 (第五届)集成电路EDA设计精英挑战赛赛程时间安排如下:

EDA设计精英挑战赛现已正式开放报名,关注官网(http://eda.icisc.cn),获取更多大赛信息。

奖项设置

关于概伦