错过直播?一文了解精准高效的标准单元库EDA解决方案NanoCell

2022-07-29

7月27日,《NanoCell精准高效的特征提取解决方案》在线研讨会火热举办,概伦电子高级首席研发工程师章胜分享了标准单元库开发挑战及单元库特征化工具。错过直播也没关系,一文带你了解概伦电子精准高效的标准单元库EDA解决方案NanoCell。

标准单元库是芯片设计的重要基础。在先进工艺下,大量Sign-Off工艺角的引入,对单元库的特征如时序、功耗、噪声及统计变化提出更高的提取要求,从而使仿真计算量呈几何级数增大,成为数字芯片设计的瓶颈。因此,单元库特征提取的效率提升是缩短开发周期的关键。

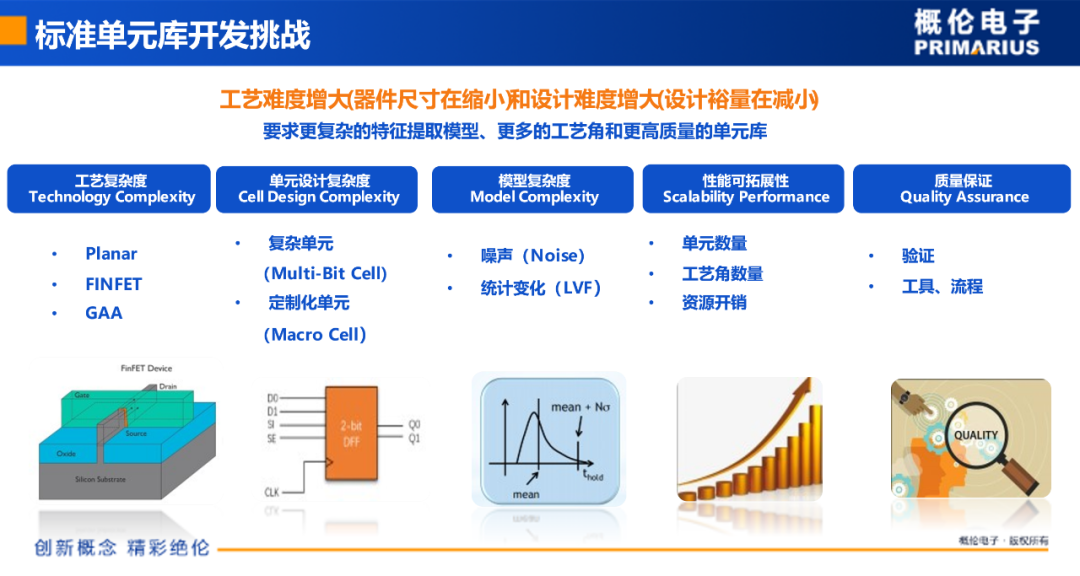

工艺难度增大,器件尺寸在缩小;设计难度增大,设计裕量在减小,这些要求更复杂的特征提取模型,更多的工艺角和更高质量的单元库。

随着晶体管的物理尺寸进入纳米级,电子迁移率降低、漏电流增大、静态功耗增大等问题层出不穷,使得新结构开发迫在眉睫。目前业界普遍的晶体管结构演化大致是22nm及以上是Planar平面晶体管结构工艺,16nm到3nm是FinFET鳍式场效应晶体管结构工艺,2nm及以下,从IMEC技术研究来看,下一代将是GAA(Gate-Around-All)环绕栅极晶体管结构工艺。

工艺和设计难度的增加,使得模型提取变得更为复杂。典型的就是先进工艺下,对于低压设计的用户需求。低压情况下,器件的Variation统计变化增大,使得在Nominal 电压下的各项设计指标正态分布变得非对称,具有长尾效应,需要更先进的LVF模型,liberty format Variation模型来对此进行建模。而LVF是通过Monte-Carlo仿真取得的结果,因此需要大量的资源开销。

为了满足多种多样的设计应用,单元的数量从几百颗增加到一千多颗,用于时序、功耗、可靠性验收的Sign-Off工艺角也由早期的几个发展到几百之多,因此需要海量的License、CPU、磁盘开销来应对挑战。

这么多库的产生,需要高质量的验证,以确保芯片的正常生成。面对这些挑战,概伦电子标准单元库特征化和验证工具应运而生。

基于概伦电子DTCO平台,立足器件建模和仿真器领域深厚的技术积累,来解决标准单元库特征提取遇到的难点和挑战。

概伦电子拥有设计和制造两大环节的核心关键工具,业界广泛认可且长期采用的Golden器件建模工具BSIMProPlus,支持7nm/5nm/3nm最新工艺及BISM3/BSIM4/BSIM6/BSIMCMG行业标准紧凑型模型;高精度、高性能SPICE仿真器NanoSpice具有最严格的精度配置且经过国际领先代工厂的严苛验证,配备高性能、轻量级调用接口。

标准单元库特征提取工具NanoCell正是基于概伦电子深厚的器件建模和仿真器技术去开发,达到高精度、高性能,简单易用的特征化工具。

NanoCell是一款快速精确且简单易用的标准单元库特征化EDA工具。通过内置的NanoSpice仿真器,采用先进的分布式并行架构技术和单元电路分析提取算法,精确且高效的对单元电路进行时序、功耗及噪声等特征进行仿真与提取,提供友好易使用的接口,帮助用户缩短产品开发周期。

较之于其他标准单元库特征化工具,NanoCell具有以下几个特点:

- 精确-内嵌高精度仿真器NanoSpice

- 快速-先进的分布式并行架构

- 易用-友好且设置简单的用户接口

- 双CPU架构支持(X86/ARM)

- 自动化单元电路分析、Arc提取

- 时序、功耗、噪声等特征仿真和提取

NanoCell在精度方面严格对标业界主流的标准:

- Timing < 1%

- Constraint < 2ps

- Power < 5%

综上所述,NanoCell支持当前业界主流的特征模型,包括NLDM、CCS、CCSN、CCSP、LVF以及Verilog;通过内置的高精度NanoSpice仿真器,模型精度达到业界标准;拥有强大的分布式并行计算能力;支持主流的HPC集群系统(SGE/LSF);同时提供ARM与X86的平台支持。NanoCell是具有高精度、高灵活性、快速易操作的多平台适用的标准单元库特征化解决方案。